International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

# **Design and Implementation of RBSD Technique for Various Arithmetic Circuits**

N.Nagaraju<sup>1</sup>, M.Rajarajeswari<sup>2</sup>, Y.Ramya<sup>3</sup>, R.Subashree<sup>4</sup>, K.Swathi<sup>5</sup>

Asst. Professor, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>1</sup>

UG Student, Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India<sup>2,3,4,5</sup>

**ABSTRACT**: In recent years, the technological developments have increased demands for arithmetic circuits with faster computation. The emergence of signed digit representation has revolutionized the digital world. Redundant binary (RB) number system is the largely used approach for indicating a signed digit number. This Number system is designed to perform high-speed operations in image processing and in DSP applications. It gives the addition without carry generation which contract the addition time of two binary numbers. The contemplated 4-bit,8-bit and 16-bit RBSD circuits are designed using VHDL and simulated using Xilinx ISE 12.3i.

**KEYWORDS**: RBSD adder, carry free addition, VHDL

## I. INTRODUCTION

Adder is the basic building block of all arithmetic operations like subtraction, multiplication, division and square root, etcthe current technological development in the field of integrated circuits with various arithmetic circuits with fast computing and carry free addition have been proposed. The Redundant binary signed digit adder(RBSD) has a greater advantages over other conventional circuits by eliminating more propagation time delay, high power consumption and complexity in operations due to carry free addition.

Mostly, fast adders are designed using ripple carry adder and carry select adder. In ripple carry adder, the propagation of carry results in critical delay. Carry select adders use ofare fast adders but it increases the length of the bit in the adder and high complexity of the circuit. The introduction of Redundant binary signed digit (RBSD) number system in designing fast adders helps to attain high-speed processing due to their ability of the technique called carry free addition. If the performance of the adder in the circuit is increased then simultaneously, the overall performance of the circuit also gets improved.

#### **II. RELATED WORK**

The most fundamental element of all the arithmetic circuits areadders. RBSD adders are immensely used to perform high speed logical operations. The RBSD number system has become more prominent due to the characteristics of carry free addition. It eliminates carry propagation chain which diminishes the processing time and improves the speed of the machine[4]. This adder is firstly fast and secondarily productive in terms of power utilization and chip area.

Shantanu Thakre, Viplav Mahajan, Shailesh Shukla proposed a system for Implementation of Fast Adder Using Redundant Binary Signed Digit. In this paper, the construction of ALU uses the technique of redundant binary signed digit(RBSD). The working of proposed ALU is broadly discussed.

Rakesh Kumar Saxena, Member IACSIT, Neelam Sharma designed the RBSD adder and multiplier circuits to execute high speed mathematical operations. In this, adder is re-modified to lower the intricacy of the circuit and the number ofgates. As we know, the process of multiplication is the constant addition, it achieves less time for executing the circuit design. Thus, the proposed RBSD adder using NOR and NAND gates will enhance the speed of digital machines[6].

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

## 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

T.N.Rajashekhara and O.Kalreported about fast multiplier design using Redundant Signed Digit numbers. In this, the less delay multiplier design is presented internally. The proposed multiplier has a multiplication time of range  $O(\log_2 x)$  and area-time complexity of range  $O(x^2 \log_2 x)$  for a word length of x[7].

#### **III. PROPOSED SYSTEM**

RBSD number representation systemshas the sufficient redundancy to permit the destruction of carryor borrow and hence the output is fast, carry freeaddition and subtraction. It is a signed digit representation and with digit set  $\{-1, 0, 1\}$ . The redundant binary representation (RBR) is a numeral system that uses A signed digit number is represented by m+n+1 digits x' (i=-n, -n+1...-1, 0, 1.....m) having algebraic value as;

Where the value of r and x' are such that the following conditions satisfied:

• The 'r' radix is a positive integer

- Algebraic value xv = 0 has unique representation

- Totally shunt addition and subtraction is probable for all digits in interrelated position of two's representation.

#### **RBSD ADDITION TECHNIQUE**

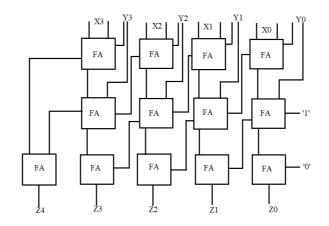

This type of adder takes a finite amount of time to generate the addition result because the carry can propagate at most one position. RBSD adder structure with a digit set (-1,0,1) per additionoperation by "Two Transfer Addition Technique" which is computed in three stages [3]i.e.:

xi + yi = 2\*t'i+1 + w'i

$$w'i + t'i = 2*t''i+1 + w''i$$

$si = w''i + t''i$

Where xi and yi = (-1, 0, 1)

t'' and t' = intermediate carry

w'' and w' = intermediate sums

Figure 1 4-Bit RBSD Adder

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

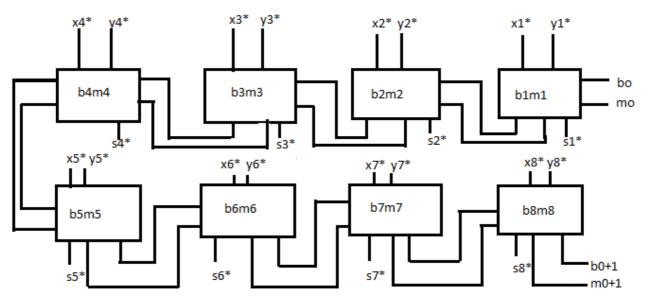

#### Figure 2 8-Bit RBSD Adder

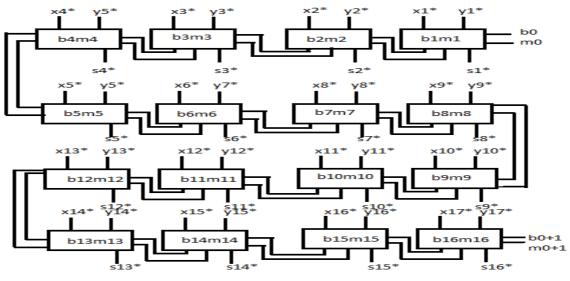

Fig 3 16-Bit RBSD Adder

#### **IV. EXPERIMENTAL RESULTS**

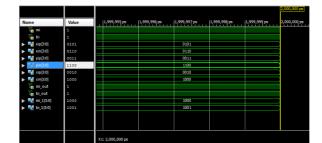

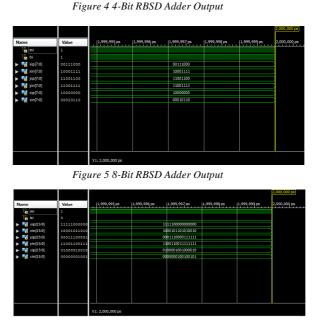

The proposed RBSD circuits are designed using VHDL and simulated using Xilinx ISE 12.3i and the simulation results of 4-bit,8-bit,16-bit Redundant Binary Signed Digit Adders are given below.

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

7<sup>th</sup> National Conference on Frontiers in Communication and Signal Processing Systems (NCFCSPS '19)

# 19<sup>th</sup>-20<sup>th</sup> March 2019

### Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Figure 616-Bit RBSD Adder Output

V. CONCLUSION

The RBSD adder has a greater advantage of constant time delay, higher speed and less complexity of the circuit. When the bit length of the inputs increased, simultaneously the efficiency of the RBSD adder will also get boosted. Therefore addition is the primary operation for all the arithmetic circuits and the fast arithmetic processors with higher bit length can be designed using RBSD architecture.

#### REFERENCES

- [1] AshishManoharraoIngale, "Redundant Radix-4 Representation with High Speed Arithmetic Co-processor Using Carry-Save and Redundant Signed Digit Technique", International Journal of Scientific and Technology Research Volume-5, issue 07, July 2016.

- [2] Smita Sharma, Akanksha Singh, KrashnKant Gupta, "Addition of Redundant Binary Signed Digits using RBSD Adder", 2015 International Conference on Futuristic Trends on Computational Analysis and Knowledge Management(ABLAZE).

[3] VandanaShukla, O.P.Singh, G.R.Mishra, R.K.Tiwari, "A novel approach to design a Redundant Binary Signed Digit Adder cell using reversible logic gates", 2015 IEEE UP Section Conference on Electrical Computer and Electronics(UPCON).

<sup>[4]</sup> SobinaGujral, RobinaGujralBagga, "Simulation Results Analysis of Basic and Modified RBSD Adder Circuits", IJISET-International Journal of Innovative Science, Engineering and Technology, Vol. 1 Issue 9, Nov 2014.

<sup>[5]</sup> ShanthanuThakre,ViplavMahajan,ShaileshShukla, "Implementation Of Fast Adder Using Redundant Binary Signed Digit", National Conference On Research In Electronics Advances & Collabrative Technologies,2013.

[6] Rakesh Kumar Saxena, Neelam Sharma and A.K.Wadhwani, "Fast Adder Design Using Redundant Binary Numbers With Reduced Chip Complexity",

<sup>[6]</sup> Rakesh Kumar Saxena, Neelam Sharma and A.K.Wadhwani, "Fast Adder Design Using Redundant Binary Numbers With Reduced Chip Complexity", IACSIT International Journal Of Engineering And Technology, vol.3, No.3, June 2011.

T.N.Rajashekhara and O.Kal, "Fast Multiplier Design using Redundant Signed Digit numbers", International Journal of Electronics, Vol 69, No 3, 359-368, 1990.